All formal verification tools, including Electrical Rules Check (ERC), must reach a trade-off between “false negatives” (i.e., real design errors that are not detected) and “false positives” (or false errors, locations where errors are erroneously reported.

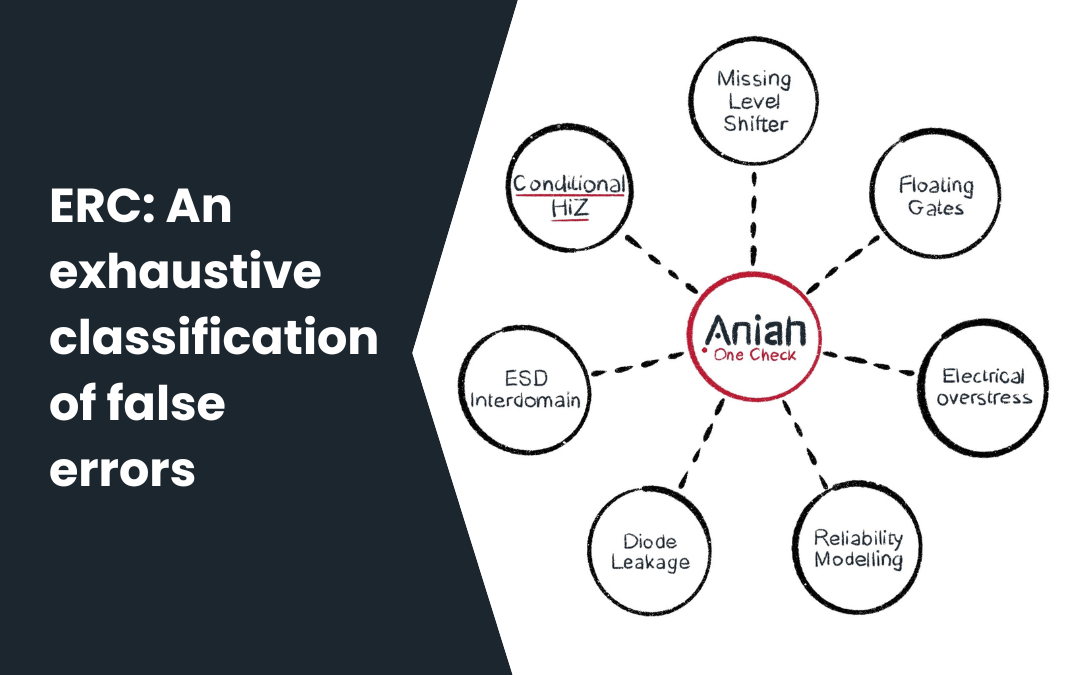

This whitepaper presents a false errors classification and root-cause analysis mechanism for efficient and reliable analysis.

We explain how Aniah OneCheck ERC verification tool takes a no-compromise approach to verification coverage; aiming to avoid false negatives, which can lead to silicon bugs.