Stories.

OneCheck® fully integrated with Cadence Virtuoso®

Oct 6, 2025 | News

Analog and mixed-signal design teams now benefit from the seamless integration of OneCheck with the industry-reference Cadence Virtuoso® Schematic Editor. Using OneCheck has never been as smooth and simple: Connect OneCheck analysis window to Virtuoso in a simple...

Aniah® keeps on improving it’s ERC solution with the Release of OneCheck V3.2.0

Mar 31, 2025 | News

We’re pleased to announce that the new version of OneCheck is here ! Version 3.2 brings the following significant improvements : View results directly in the schematic you’re familiar with, thanks to a reworked and powerful back-annotation mechanism in Cadence’s...

Aniah® wins iVenture prize at Tech&Fest 2025

Aniah took part for the second time in the Tech & Fest trade fair, held in Grenoble on 5 and 6 February 2025. This event, now a must for innovation in Europe, brings together researchers, investors and entrepreneurs. Over the two days, iForum gave Aniah the...

Just Three Months After V3.0, Aniah® Announces the Release of OneCheck V3.1.0

Nov 13, 2024 | News

We’re please to announce that the new version of OneCheck is here ! Version 3.1.0 brings major enhancements to OneCheck, including : Greatly improved error detection and clustering heuristics New integrity checking functionality Management of double dependencies in...

The Aniah® 2024 team-building day

November 8th, Aniah joined the Vercors plateau and enjoyed a memorable day of team building, reinforcing the leadership of each team member through various activities to bring real strength to the OneCheck project and develop our future ambitions.

Aniah® announces the release of OneCheck V3.0

Jul 15, 2024 | News

We’re please to announce that the new version of OneCheck is here ! The 3.0 version focuses on : SmartClustering by root cause: Smart algorithms categorize issues by priority, then cluster them by underlying root causes Description of the error is made in...

Design Automation Conference 2024

After participating in DAC 2023, Aniah was delighted to take part for a second time in the Design Automation Conference (DAC) in San Francisco from 23 to 27 June 2024. This not-to-be-missed event enabled us to discover the latest technological advances, exchange ideas...

Aniah® Ignites Global Expansion with Strategic Partnerships

May 24, 2024 | News

We are thrilled to unveil groundbreaking partnerships that will catapult Aniah's international growth to unprecedented heights! These strategic alliances mark a pivotal moment in our journey, one that will accelerate our development and reinforce our commitment to...

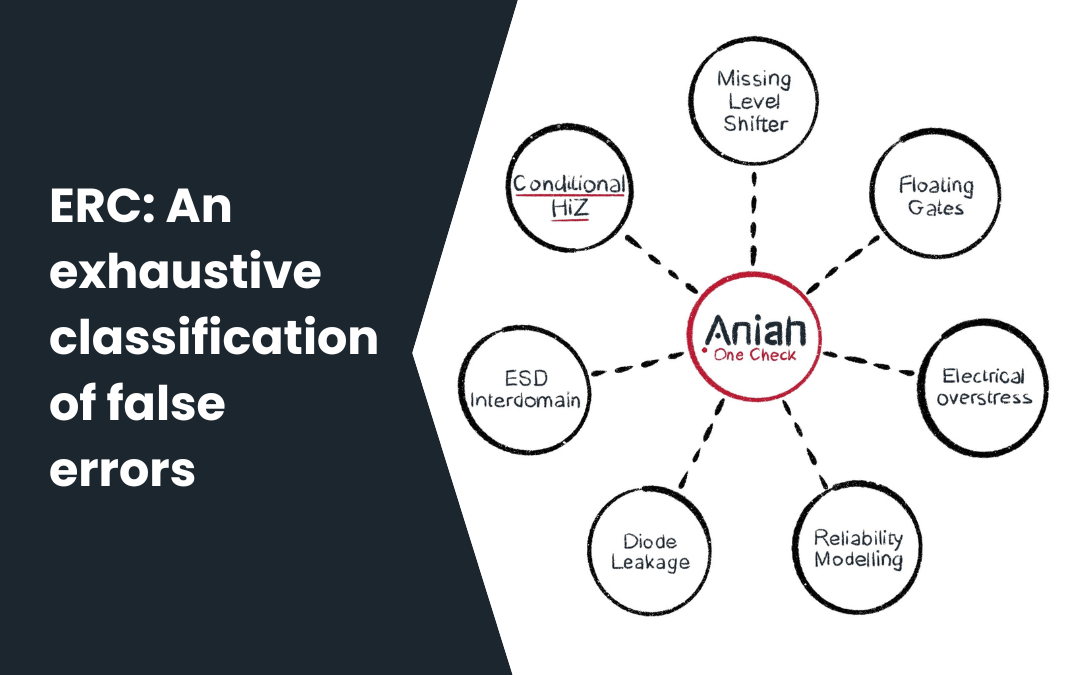

ERC: An exhaustive classification of false errors

Apr 11, 2024 | Whitepapers

All formal verification tools, including Electrical Rules Check (ERC), must reach a trade-off between “false negatives” (i.e., real design errors that are not detected) and “false positives” (or false errors, locations where errors are erroneously reported. This...

“A Transistor Level Relational Semantics For Electrical Rule Checking By SMT Solving” – DATE 2024

Mar 13, 2024 | Events

A short presentation of the paper "A Transistor Level Relational Semantics For Electrical Rule Checking By SMT Solving", accepted at: Design, Automation and Test in Europe conference (DATE 2024). The paper introduces a formal approach to model circuits' steady-states...

ANIAH® and PROPHESEE Announce Collaboration

Feb 8, 2024 | Press releases

ANIAH and PROPHESEE Announce Collaboration to strengthen their technological synergies. PARIS, February 8, 2024 PROPHESEE, the creator of the world’s most advanced and efficient neuromorphic vision systems, in his constant search for operational excellence, has...

Aniah® celebrates France 2030 recognition

Jan 31, 2024 | News

Aniah celebrates France 2030 recognition and affirms its commitment to contributing to the independence and resilience of the European microelectronics industry. Grenoble, January 30, 2023, Aniah is delighted to share the double recognition from the French...

Aniah® announces that it has joined AENAS

Jan 22, 2024 | News

Aniah is proud to announce her membership of the AENEAS association (https://aeneas-office.org), allowing us to integrate into this unique ecosystem which bring in together more than 550 members: SMEs, Research Institutes and Universities, Large Industry from the...

Aniah® awarded Startup of the Year by ElectroniqueS magazine

Nov 30, 2023 | News

On November 28, 2023, the Alliance des Composants et Systèmes pour l'Industrie Electronique, #ACSIEL and ElectroniqueS magazine awarded Aniah for the trophy "Startup of the Year". The ceremony took place at the association's headquarters in Paris, in the...

Aniah® validates both ISO9001 and ISO27001 certifications

Oct 30, 2023 | Press releases

Aniah is proud to announce its recent success in obtaining both ISO9001 and ISO27001 certifications. These two achievements mark a significant step forward in the company's quality and cybersecurity development plans. Read all about it in our press release !

Aniah® at CadenceLIVE Taiwan

Jul 31, 2023 | Events

Come meet us at CadenceLive Taiwan ! We're pleased to meet you on August 31, 2023 at Zhubei, Hsinchu, Taiwan for the CadenceLive Taiwan. See you there !

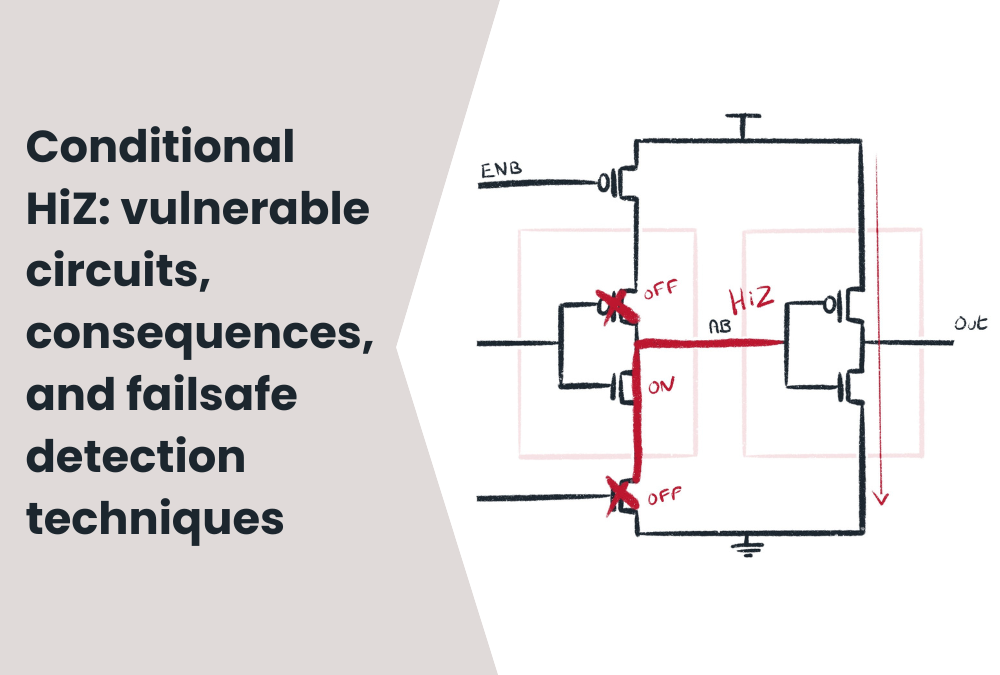

Conditional High Impedance Nets : Early detection in analog and digital topologies

Jul 10, 2023 | Whitepapers

Conditional high-impedance (HiZ) nets errors are among the most serious risks in an IC project because of their capacity to elude Silicon qualification phases and escape into mass-production. They may create a wide range of issues throughout the Validation,...

Aniah® joins Cadence Connections Programs

Oct 14, 2022 | News

Aniah is proud to announce joining Cadence’s Connections Program earlier this year in May 2022. Our verification tool can now easily connect to Cadence Virtuoso Schematic Editor ®. From now on, our customers will be able to use Aniah ERC tool to check for errors and...

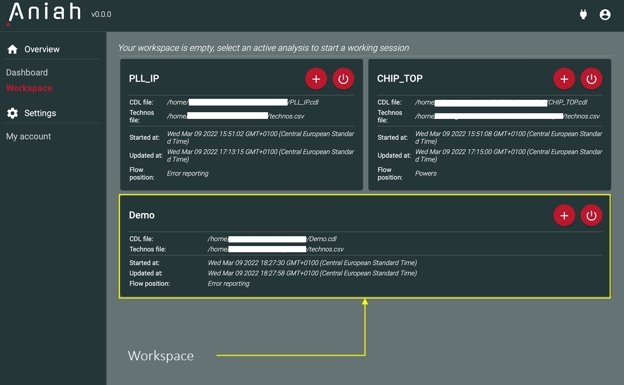

Aniah® Software V2.1

Oct 14, 2022 | Press releases

This summer, our development team worked on the latest version of Aniah V2.1 ! It includes 4 brand-new features, for an easier use : – Synoptic schematic – Advanced-Power-Analysis – Verilog netlist support – Topology detection for a better precision This new version...

Aniah® Software V2.0 Deployment

Apr 8, 2022 | Press releases

The V2.0 has been released ! This release provides the full potential of electrical rules checking (ERC) while offering unprecedented ease of use. Its main assets are : – Comprehensive set of ERC rules natively supported. – Unparalleled performances and scalability. –...

Magnify the Traditional Mixed-Signal Eyepatch Verification

Apr 20, 2021 | Whitepapers

Weeks before tapeout, SoC design teams must verify large mixed-signal transistor-level netlists. The standard approach is to verify functionality by running simulations with back-annotated gate-level RTL along with behavioral analog blocks. However, since this...

French Tech Emergence status awarded to Aniah®

Nov 23, 2020 | News

In June 2020, the French Tech Emergence grant was awarded to Aniah. The French Tech Emergence grant is aimed at supporting Deeptech start-ups. BPI France evaluated Aniah’s technology and value proposition and concluded that Aniah, as a company, has strong growth...

ERC: a trade-off between coverage and false positives?

Oct 12, 2020 | Whitepapers

Electrical Rule Checking (ERC) solutions face a double challenge: handle the billions of transistors of a chip and be accurate enough to detect all failure modes. Any solution that doesn’t have a good understanding of the function of each transistor and the electrical...

Electrical errors in ICs: why they occur and their consequences

Sep 29, 2020 | Whitepapers

The verification of electrical errors at chip-level has always been the missing step in chip design closure – even though a chip is, basically, a very large circuit. The complexity of such an analysis has so far made it impossible. Consequently, considerable effort is...