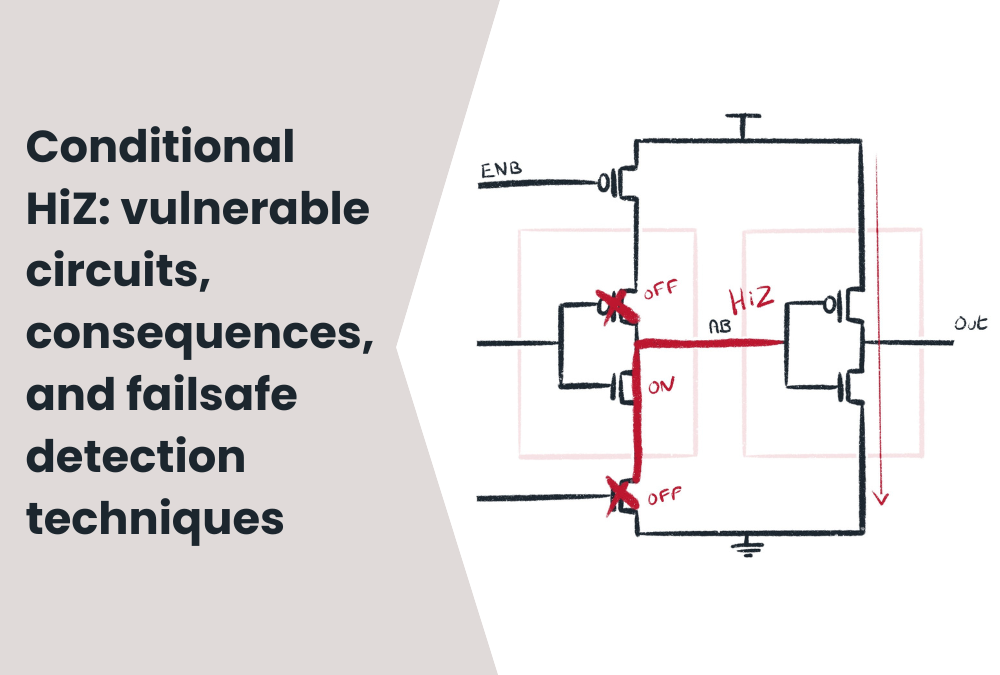

Conditional high-impedance (HiZ) nets errors are among the most serious risks in an IC project because of their capacity to elude Silicon qualification phases and escape into mass-production. They may create a wide range of issues throughout the Validation, Qualification and Ramp-up of an IC design.

This paper reviews the different types of circuit topologies that can lead to potentially harmful HiZ and reliable techniques to detect those errors at SoC scale with a very reduced human resource investment.

Aniah® keeps on improving it’s ERC solution with the Release of OneCheck V3.2.0

We’re pleased to announce that the new version of OneCheck is here ! Version 3.2 brings the following significant improvements : View results directly in the schematic you’re familiar with, thanks to a reworked and powerful back-annotation mechanism in Cadence’s...