Whitepapers.

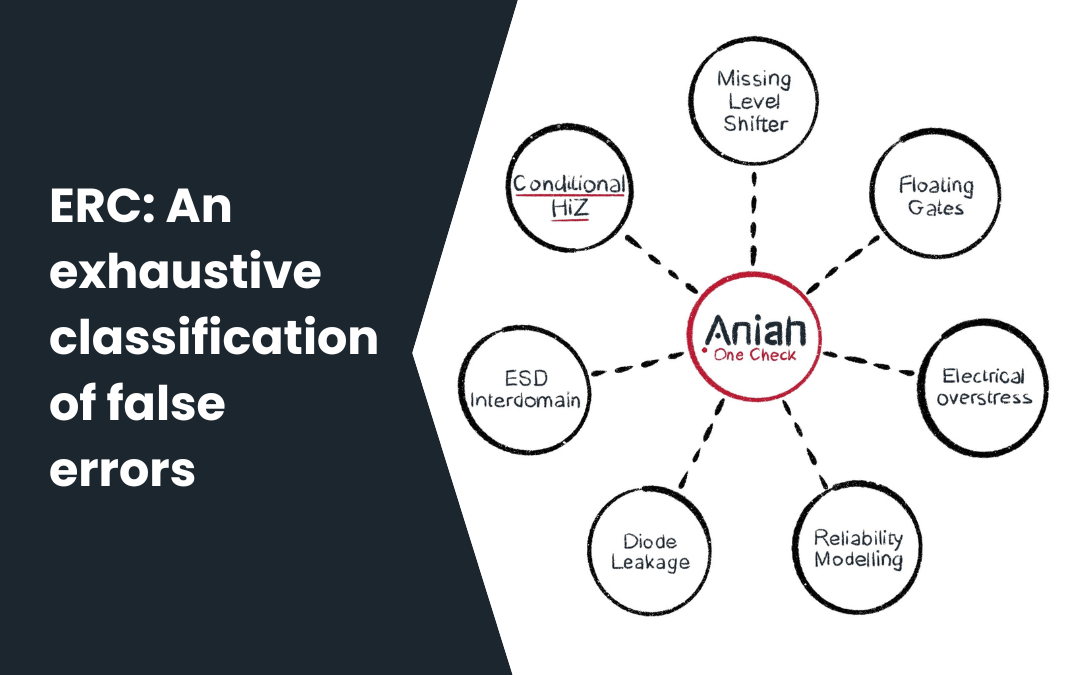

ERC: An exhaustive classification of false errors

Apr 11, 2024 | Whitepapers

All formal verification tools, including Electrical Rules Check (ERC), must reach a trade-off between “false negatives” (i.e., real design errors that are not detected) and “false positives” (or false errors, locations where errors are erroneously reported. This...

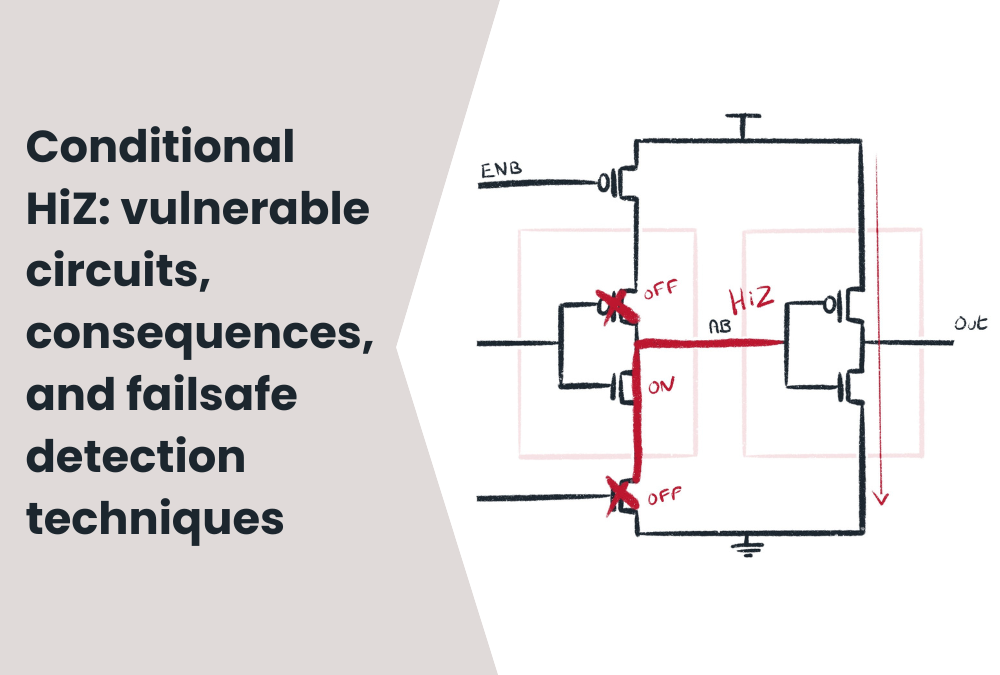

Conditional High Impedance Nets : Early detection in analog and digital topologies

Jul 10, 2023 | Whitepapers

Conditional high-impedance (HiZ) nets errors are among the most serious risks in an IC project because of their capacity to elude Silicon qualification phases and escape into mass-production. They may create a wide range of issues throughout the Validation,...

Magnify the Traditional Mixed-Signal Eyepatch Verification

Apr 20, 2021 | Whitepapers

Weeks before tapeout, SoC design teams must verify large mixed-signal transistor-level netlists. The standard approach is to verify functionality by running simulations with back-annotated gate-level RTL along with behavioral analog blocks. However, since this...

ERC: a trade-off between coverage and false positives?

Oct 12, 2020 | Whitepapers

Electrical Rule Checking (ERC) solutions face a double challenge: handle the billions of transistors of a chip and be accurate enough to detect all failure modes. Any solution that doesn’t have a good understanding of the function of each transistor and the electrical...

Electrical errors in ICs: why they occur and their consequences

Sep 29, 2020 | Whitepapers

The verification of electrical errors at chip-level has always been the missing step in chip design closure – even though a chip is, basically, a very large circuit. The complexity of such an analysis has so far made it impossible. Consequently, considerable effort is...